Introduction

Interrupts are a fundamental part of modern computer systems, allowing for devices and programs to communicate with each other in real time. Interrupts are signals sent by hardware devices or software programs to the processor, indicating that a specific event has occurred and requiring the processor’s immediate attention. Interrupts can be triggered by a variety of events, such as user input, a system timer, or data arriving from a network. Interrupt handling is the process of managing these interrupts and responding to them in a timely and efficient manner.

Types of Interrupts

There are two main types of interrupts: hardware interrupts and software interrupts.

Hardware interrupts are triggered by external events, such as a keypress on a keyboard or a data transfer from a network interface card. Hardware interrupts are usually handled by the operating system, which has a set of interrupt handlers that are specific to each hardware device. When a hardware interrupt is triggered, the processor saves its current state and jumps to the appropriate interrupt handler, which then processes the interrupt and returns control to the operating system.

Software interrupts, on the other hand, are triggered by software programs, typically to request a service from the operating system. For example, a program may request that the operating system allocate memory or perform a file I/O operation. Software interrupts are usually handled by the operating system’s system call interface, which provides a standard interface for programs to request services from the operating system.

Interrupt Handling Process

The interrupt handling process consists of several steps:

- Interrupt request: The device or program sends an interrupt request to the processor.

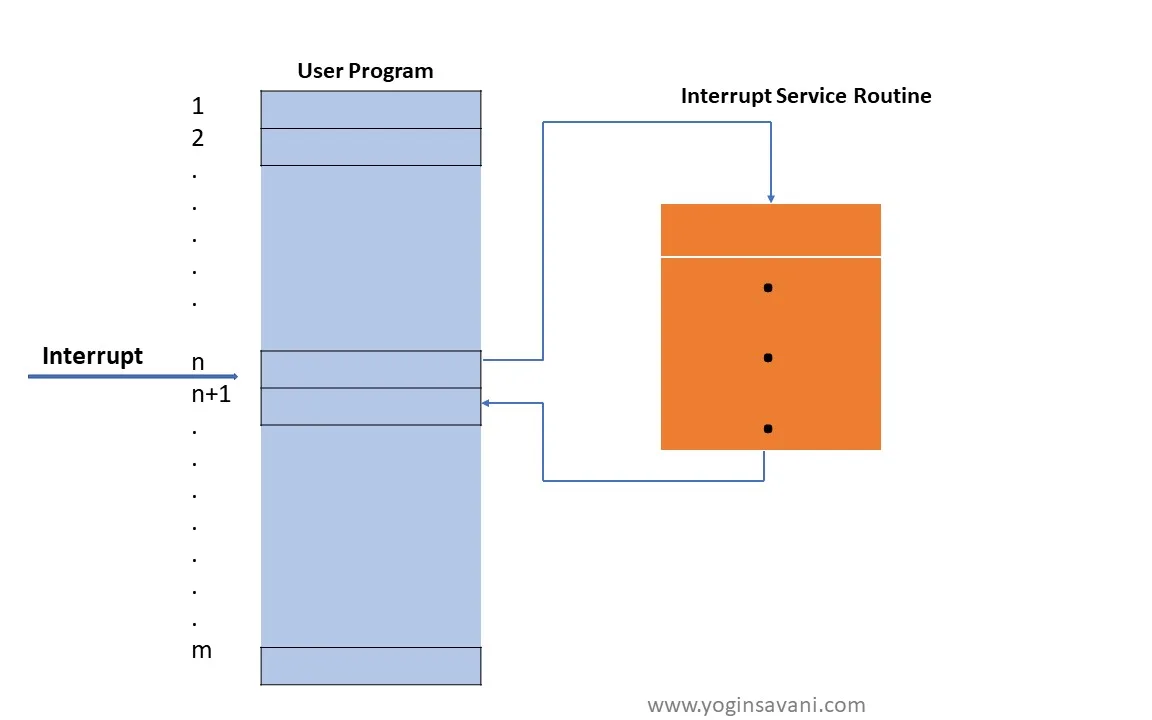

- Interrupt service routine (ISR): The processor saves its current state and jumps to the appropriate ISR. The ISR is a piece of code that handles the interrupt and performs any necessary actions.

- Interrupt masking: While the ISR is executing, the processor may mask (disable) other interrupts to prevent them from interfering with the current ISR.

- Interrupt acknowledgment: Once the ISR is complete, the processor sends an acknowledgment signal to the device or program to indicate that the interrupt has been handled.

- Interrupt unmasking: The processor then unmasks (enables) any interrupts that were previously masked.

- Return from ISR: The processor returns to the point in the program where it was interrupted and continues executing.

Interrupt Handlers and Interrupt Service Routines

Interrupt handlers and interrupt service routines (ISRs) are two terms often used interchangeably, but they refer to slightly different things. Interrupt handlers are the software routines responsible for managing the flow of interrupts in the operating system. They typically run in kernel mode and are responsible for saving the context of the interrupted program and transferring control to the appropriate ISR.

ISRs, on the other hand, are the routines that actually perform the necessary processing in response to the interrupt. They are typically short and focused on handling a specific event. Once the ISR has completed its task, it returns control to the interrupt handler, which restores the context of the interrupted program and returns control to the program.

Interrupt handlers and ISRs are often written in assembly language or low-level languages such as C, as they require precise control over system resources and timing.

Interrupt Priorities

Interrupts can have different levels of priority, which determines the order in which they are processed. Interrupt priority is an essential consideration in real-time systems, where timely response to critical events is essential.

In some systems, interrupt priorities are fixed, while in others, they can be dynamically assigned. Interrupt priority can be managed by hardware, software, or a combination of both. Some systems use multiple levels of interrupt priority, with higher-priority interrupts preempting lower-priority interrupts.

Interrupt priority can be managed using a variety of techniques, such as priority queuing, round-robin scheduling, and priority inversion avoidance.

Interrupt Latency and Real-Time Systems

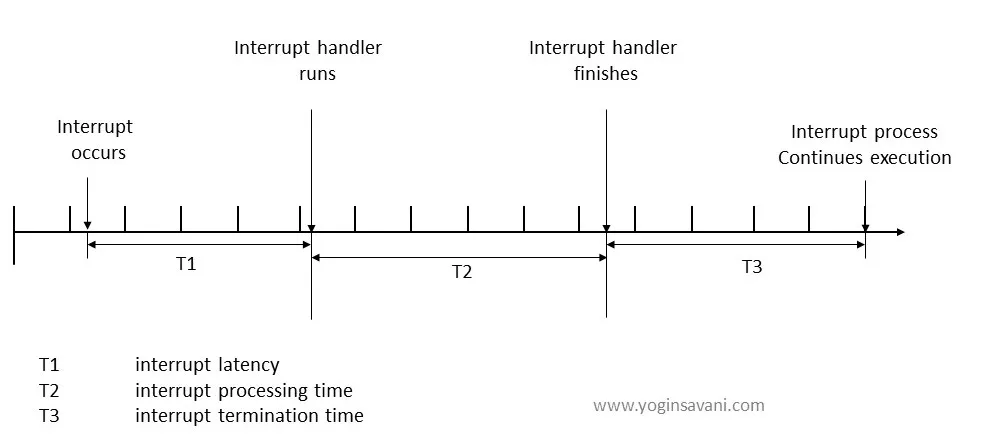

Interrupt latency is the time it takes for a system to respond to an interrupt. In real-time systems, where timely response to critical events is essential, minimizing interrupt latency is a critical consideration.

Interrupt latency can be affected by a variety of factors, including hardware design, interrupt handling software, and system load. Designing hardware and software that minimizes interrupt latency is a key consideration in real-time system design.

Interrupt Latency Reduction Techniques

Several techniques can be used to reduce interrupt latency, including:

- Interrupt coalescing: This technique involves aggregating multiple interrupts into a single interrupt to reduce the overhead associated with interrupt handling.

- Interrupt preemption: This technique involves interrupting lower-priority interrupts to process a higher-priority interrupt.

- Interrupt prioritization: This technique involves assigning priorities to interrupts and processing higher-priority interrupts first.

- Hardware design: Hardware can be designed to minimize interrupt latency by providing dedicated interrupt handling hardware or reducing the time it takes to respond to an interrupt request.

Conclusion

Interrupt handling is a critical aspect of modern computer systems, enabling devices and programs to communicate with each other in real time. Interrupt handlers and ISRs are responsible for managing and processing interrupts, respectively. Interrupt priority and interrupt latency are essential considerations in real-time system design. Interrupt coalescing, interrupt preemption, interrupt prioritization, and hardware design are all techniques that can be used to reduce interrupt latency and improve system performance. By understanding the principles of interrupt handling, developers can create efficient and reliable systems that meet the demands of modern computing.

Read My Other Blogs:

Embedded C language Interview Questions.

Automotive Interview Questions