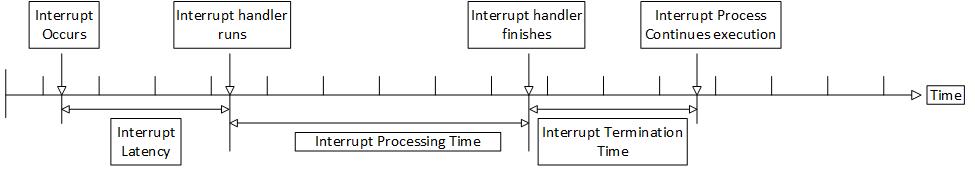

Interrupt latency is a crucial metric in computing systems, especially for those requiring real-time performance, such as embedded systems, automotive controllers, and industrial automation. It measures the time taken by a system to respond to an interrupt request. Low interrupt latency is essential for meeting strict timing requirements in these systems. This post will explain interrupt latency, its components, and its relationship to the interrupt handling process, as illustrated in the timeline provided.

Interrupt Handling Timeline

To understand interrupt latency, let’s walk through each phase of the interrupt handling process as shown in the timeline:

- Interrupt Occurs

This is the point in time when an interrupt signal is generated, typically by an external event or an internal condition that requires immediate attention. The moment an interrupt is detected, the system starts its interrupt-handling procedure. - Interrupt Latency

Interrupt Latency is the time between when the interrupt occurs and when the interrupt handler begins executing. This delay can include:- Recognition time for the interrupt signal.

- Time taken to determine if the interrupt is masked or if a higher-priority task is running.

- Context-saving operations and mode switching, if needed. The lower the interrupt latency, the faster the system can respond to events, which is especially critical in time-sensitive applications.

- Interrupt Handler Runs

This phase starts as soon as the interrupt latency period ends. Here, the Interrupt Service Routine (ISR) or handler executes to address the cause of the interrupt. The ISR performs actions like reading sensor data, initiating a response, or setting a flag for the main program. - Interrupt Processing Time

Interrupt Processing Time is the duration the CPU spends executing the ISR. This phase is directly related to how quickly the system can process the interrupt. Keeping this phase as short as possible is essential to avoid long interruptions in the main task execution. Efficient ISR design, with minimal tasks offloaded to the main process, helps minimize this time. - Interrupt Handler Finishes

Once the ISR completes its operations, the system needs to restore the saved context and possibly switch modes back to user or application mode. This marks the end of interrupt handling for this specific event. - Interrupt Termination Time

Interrupt Termination Time is the period from when the interrupt processing finishes until the system resumes normal execution of the interrupted task. This phase includes tasks like restoring the previous execution context. The combination of interrupt latency, interrupt processing time, and interrupt termination time determines the overall impact of the interrupt on system performance. - Interrupt Process Continues Execution

After all interrupt-related processing is completed, the system resumes execution of the previously interrupted task. This signifies the end of the interrupt handling cycle.

Key Components Influencing Interrupt Latency

Using this timeline, we can better identify factors that influence each component of interrupt latency and processing time:

- Hardware and CPU Architecture

- Recognition Time: Faster CPUs and dedicated interrupt controllers (such as ARM’s Nested Vectored Interrupt Controller, or NVIC) can quickly recognize and prioritize interrupts, reducing recognition time.

- Bus Speed and Memory Access: High-speed buses and fast memory access help reduce the time taken for context-saving and retrieval.

- Operating System and ISR Design

- Interrupt Masking and Prioritization: Efficient interrupt prioritization and minimal interrupt masking are essential. By allowing high-priority interrupts to preempt lower-priority ones, systems can handle critical events faster.

- Efficient Context Saving: Optimized OS routines for saving and restoring context contribute to reduced interrupt latency and termination time.

- ISR Complexity: Short and efficient ISRs minimize the interrupt processing time, helping keep the overall interrupt handling time within acceptable limits.

- System Load and Resource Contention

- CPU Load: A high CPU load can delay both the recognition of interrupts and the handling process, increasing latency.

- Cache and Memory Usage: Memory-heavy processes can increase delay due to cache misses, particularly affecting context-switching time.

Strategies to Minimize Interrupt Latency and Processing Time

- Optimize ISR Code

Keep ISRs as short and efficient as possible. Offload complex tasks to the main program logic or background tasks to reduce interrupt processing time and allow the system to quickly return to the interrupted task. - Leverage Direct Memory Access (DMA)

Use DMA to handle data transfers without involving the CPU. This allows time-sensitive tasks, like data collection from sensors, to occur independently of interrupt handling, reducing interrupt processing time. - Reduce Interrupt Masking

Avoid extensive periods of interrupt masking. Only disable interrupts when absolutely necessary and re-enable them as soon as possible to reduce interrupt latency. - Use Hardware Interrupt Prioritization

Implement hardware-based interrupt prioritization to ensure critical interrupts preempt less important tasks, reducing the overall impact on interrupt latency and termination time. - Tune the Operating System

If using a Real-Time Operating System (RTOS), configure it to minimize context-switching overhead and allow preemptive interrupt handling. Some RTOS configurations provide direct options for managing interrupt latency and priority settings.

Conclusion

In real-time and embedded systems, understanding and minimizing interrupt latency, processing time, and termination time is crucial for meeting stringent timing requirements. By optimizing each phase of the interrupt-handling timeline—latency, processing, and termination—engineers can ensure that their systems are responsive and reliable.

This timeline-based breakdown of interrupt handling offers a clearer understanding of each component, making it easier to identify optimization opportunities. In applications ranging from automotive systems to medical devices, minimizing interrupt latency is key to achieving safe, efficient, and reliable system behavior.

Read my other blogs:

Understanding JTAG Security in Embedded Systems: Risks and Best Practices

C Program to find Given Number is Prime or not.

The Internet of Things (IoT): The Connected World

Write a program to find Factorial Numbers of a given numbers.

Embedded C language Interview Questions.

Automotive Interview Questions

Understanding AUTOSAR Architecture: A Guide to Automotive Software Integration

Big Endian and Little Endian in Memory

Zero to Hero in C language Playlist

Embedded C Interview Questions

Subscribe my channel on Youtube: Yogin Savani